- 机器人、自动化、工业信息技术

- 工业软件

- 设计软件

- SIEMENS EDA/西门子

分析软件 Aprisa质量设计数据库

添加到我的收藏夹

添加到产品对比表

产品规格型号

- 功能

- 分析, 质量, 设计, 数据库, 优化

- 应用

- 流程, 建筑

产品介绍

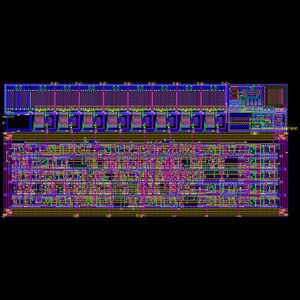

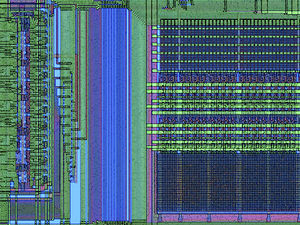

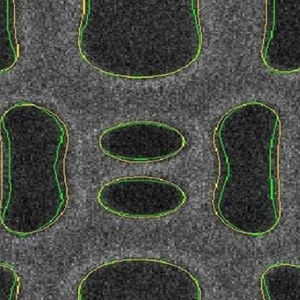

在先进工艺节点上进行设计,需要一种新的布局布线范式来管理日益增加的复杂性。Aprisa 是面向现代 SoC 的以细节路由为中心的物理设计平台。

利用布局布线技术加速 SoC 设计

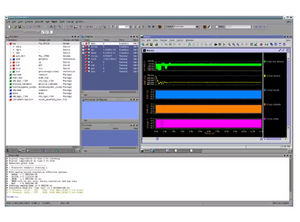

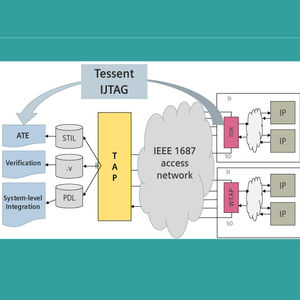

Aprisa 数字实现是一种 RTL2GDSII 解决方案,可为顶层分层设计和块级实现提供完整的综合和布局布线功能。它的带出质量与签核工具(STA 时序和 DRC)相关,可减少设计闭合时间,确保最佳性能、功耗和面积 (PPA)。

使用 Aprisa SoC 设计软件的优势?

Aprisa 提供開箱即用的最佳 PPA。這有助於實體設計人員減少佈局流程中每個步驟的工作量,加快產品上市時間。

快速完成設計

统一的架构和通用的分析引擎确保了实现步骤之间以及与签核工具之间出色的时序和 DRC 关联性,大大减少了流程迭代和 ECO 的次数

人工智能技术帮助设计人员完成任务

人工智能驱动的自动宏布局 (AMP) 技术可在极短的时间内提供专家级设计质量的宏布局

无与伦比的开箱即用 PPA

Aprisa 以細部路由為中心的架構,可在貼片和 CTS 過程中,透過參考流程消除對貼片群組或邊界的需求,提供出色的開箱即用結果。

最佳拥有成本

已通过主要代工厂最先进节点的认证、

同时支持成熟节点。Aprisa 是最容易采用的数字实现解决方案,也是最有效的工程和计算资源解决方案

---

PDF产品目录

该产品还没有PDF产品手册

查看SIEMENS EDA的所有产品目录