- 机器人、自动化、工业信息技术

- 工业信息化

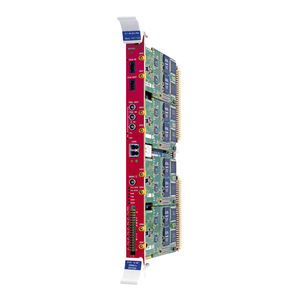

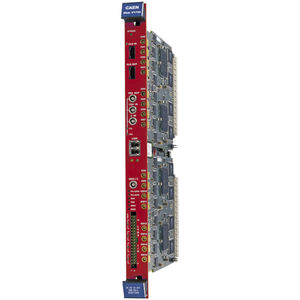

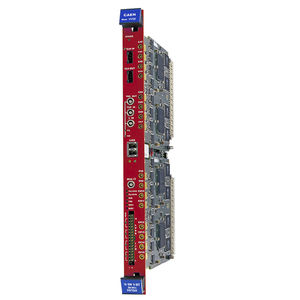

- PCIe模数转换器

- CAEN Spa

最高62.5MS/s模数转换器 64通道12位PCIe

添加到我的收藏夹

添加到产品对比表

产品规格型号

- 传送速度

- 最高62.5MS/s

- 通路数量

- 64通道

- 技术参数

- 12位, PCIe, VME

产品介绍

V1740 是一个 1 单元宽的 VME 6U 模块,内含一个 64 通道 12 位 62.5 MS/s(使用外部时钟时为 65 MS/s)闪存 ADC 波形数字化仪,在两个 ERNI SMC 连接器上具有 2 Vpp 单端输入动态范围。还提供输入满量程范围为 10 Vpp(单端)的版本(V1740A/V1740C)。

通过可编程 16 位 DAC(每个 8 通道组一个)进行直流偏移调整(范围为 ±1 V / 5 V),可对双极性(Vin = ±1 V / 5 V)至全正(Vin = 0 ÷ +2 V / 10 V)或负(vin = 0 ÷ -2 V / 10 V)模拟输入摆幅进行正确采样,而不会损失动态分辨率。

该模块具有前面板时钟输入和输出以及一个 PLL,用于从内部/外部基准合成时钟。数据流连续写入循环内存缓冲器。当触发发生时,FPGA 会再写入 N 个采样点用于后触发,并冻结缓冲区,该缓冲区可通过 VMEbus 或光纤链路读取。在新的缓冲区中,采集可以无死角地继续进行。

每个通道都有一个 SRAM 多事件缓冲器,可分为 1 ÷ 1024 个可编程大小的缓冲器。冻结缓冲区的读出(通过 VMEbus 或光链路)独立于活动缓冲区(ADC 数据存储)的写入操作。通过订购选项,可提供两种大小的通道数字存储器:192 kS/ch(V1740/V1740C 型)和 1.5 MS/ch(V1740A/V1740B 型)。

V1740 支持多板同步,允许所有 ADC 同步到一个共同的时钟源,并确保触发时间戳对齐。同步后,所有数据都将在多个 V1740 板上保持一致和连贯。

---

PDF产品目录

该产品还没有PDF产品手册

查看CAEN Spa的所有产品目录* 显示价格为参考价,此价格不含税、不含运费、不含关税,也不包含因安装或投入使用所产生的其他额外费用。参考价格可能因国家、原材料价格和汇率的不同而产生变化。