- 电学、电子和光学设备

- 电子元件

- 32位微控制器

- ADI/凌力尔特

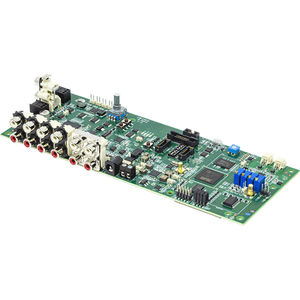

32位微控制器 ADSP-21567 series车用通用模拟

添加到我的收藏夹

添加到产品对比表

产品规格型号

- 类型

- 32位

- 应用

- 通用, 车用

- 其他特性

- 模拟

产品介绍

SHARC+内核基础架构

600MHz(最大值)或800MHz(最大值)内核时钟频率

640KB片内1级(L1) SRAM存储器(支持奇偶校验)提高了低延迟性能

支持32、40和64位浮点

32位定点

字节、短字、字、长字寻址

存储器

512KB片内2级(L2) SRAM,具有ECC保护功能,在许多用例中无需外部存储器

一个针对低系统功耗而优化的3级(L3)接口,提供与DDR3(支持1.35 V DDR3L器件)SDRAM器件相连的16位接口

16位DDR/DDR3L存储器控制器

DDR3L支持1.35V

高级硬件加速器

增强型FIR/IIR加速引擎以内核时钟频率运行,可提高处理能力

带OTP的安全加密引擎

强大的DMA系统

创新型数字音频接口(DAI)包括:

8个全SPORT接口(提供TDM和I2S模式)

2个S/PDIF Rx/Tx、8个ASRC对

4个精密时钟发生器

28个缓冲

其他外设连接/接口:

2个四通道SPI、1个八通道SPI

MLB 3引脚

6个I2C、3个UART

2个链路端口

10个通用定时器、1个通用计数器

2个看门狗定时器

4通道12位管理ADC

40个GPIO引脚、28个DAI引脚

热传感器

封装

17mm x 17mm(0.8mm间距)400引脚CSP_BGA封装

其他特性

安全和保护

加密硬件加速器

快速安全引导,支持IP保护

以1 GHz运行的增强FIR和IIR加速器

通过AEC-Q100汽车应用认证

PDF产品目录

该产品还没有PDF产品手册

查看ADI的所有产品目录